# Embedded DC-DC Converters Using ISL6520 and ISL6520A PWM Controller ICs

Application Note May 2001 AN9932

Author: Doug Mattingly

#### Introduction

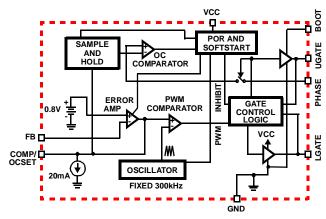

The ISL6520 and the ISL6520A are voltage mode controllers with many functions that are needed for a multitude of demanding applications. The ISL6520 and ISL6520A contain a high performance error amplifier, a high accuracy reference, a fixed 300kHz internal oscillator and over-current protection circuitry. There are two MOSFET drivers for use in synchronous-rectified Buck converters. The ISL6520A is also capable of regulating the output voltage while the DC-DC converter is sinking current. All these features are packaged in a small 8 pin SOIC. More complete descriptions of the ISL6520 and the ISL6520A can be found in their respective datasheets [1,2].

This application note details the ISL6520 and ISL6520A in DC-DC converters for applications requiring a tightly regulated, fixed output voltage. Any low-cost application requiring a DC-DC converter can benefit from one of the designs presented in this application note

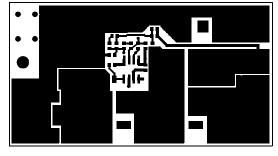

FIGURE 1. ISL6520 BLOCK DIAGRAM

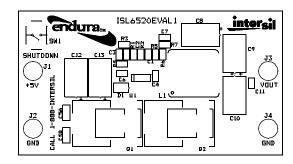

# ISL6520 Reference Design

The ISL6520EVAL1 is an evaluation board that highlights the operation of the ISL6520 in an embedded application. The evaluation board is populated with the ISL6520 controller IC, however, the designer may evaluate the ISL6520A simply by removing the ISL6520 IC and replacing it with the ISL6520A. The ISL6520EVAL1 is flexible enough to allow for reference designs with 5A, 10A, and 15A output currents at a fixed output voltage of 3.3V. A simple resistor change allows the output to go as low as 0.8V to as high as the input voltage. This flexibility allows a power supply designer to easily modify an existing design to suit almost any relevant application. The ISL6520EVAL1 DC-DC converter demo boards are customized to provide up to 15A of current at a fixed output voltage. The circuit configurations described in this application note refer to the demo board customized to

15A, unless otherwise noted. The schematic, Bill of Material, and Board Layout for the ISL6520EVAL1 can be found in the appendix. Customization of the reference design is discussed below.

#### Quick Start Evaluation

The input to the ISL6520EVAL1 board will only accept 5V from a standard power supply. The outputs can be exercised using either resistive or electronic loads. The shutdown switch, SW1, will allow the designer to evaluate how the ISL6520 shuts down and starts up. Pressing the switch will shut the converter down while releasing it will allow the converter to restart.

### Startup

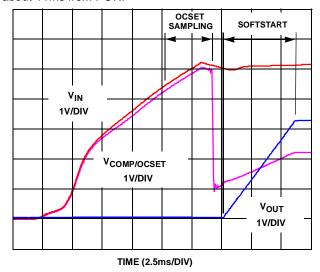

The ISL6520 and the ISL6520A have identical start up sequences. Figure 2 shows a typical start up sequence. Once the input voltage has exceeded the Power On Reset (POR) threshold level, the IC will begin it's start up sequence.

First, the error amplifier is disabled allowing 20µA of current to be drawn through a resistor tied between  $V_{CC}$  and the COMP/OCSET pin. The voltage that is impressed across the resistor is then read and sampled at the COMP/OCSET pin, with respect to  $V_{CC}$ . It is then held in internal memory as the overcurrent set point used in the upper MOSFET  $R_{DS(on)}$  overcurrent sensing feature.

After the overcurrent set point is established, the error amplifier is re-enabled and the ISL6520 then initiates it's soft start sequence through the use of an internally generated soft start ramp. The entire start up procedure typically takes about 11ms from POR.

FIGURE 2. SYSTEM STARTUP

### Shutdown and Restart

DC-DC converters that utilize the ISL6520 or the ISL6520A may be shut down by pulling the COMP/OSCET pin below 0.8V. One method to implement this feature is to connect the drain of a source grounded small signal MOSFET to the COMP/OSCET pin so that an external signal may trigger the command. The regulator will react to the shutdown command by pulling both of the MOSFET gates to ground, thus shutting down the converter.

The ISL6520EVAL1 board demonstrates the shutdown feature with a push button. Depressing the push button will disable the converter by pulling the COMP/OSCET pin to ground. Once released, the converter will follow it's normal start up procedure, which includes the overcurrent set point programming and soft-start.

#### Reference Design Customization

The ISL6520EVAL1 evaluation board was designed to be as flexible as possible for the power supply designer. The board will accommodate either DPAK or D2PAK packaged MOSFETs in the same footprint and in either the upper or lower MOSFET locations. This allows for a wide range of power levels on the same board. The designer may also implement either a Type II or a Type III compensation network. Finally, there are component locations in place that allow the designer to incorporate output voltage droop into the design.

Table 1 presents reference values for three different converter designs that may be used on the ISL6520EVAL1 board. The reference designs are optimized for 5A, 10A, and 15A maximum output capabilities. For further customization, recommended guidelines for component selection are included below.

### Input Capacitor Selection

The number of input capacitors and their capacitances are usually determined by their maximum RMS current ratings. A conservative approach to determining the number and type of input capacitors is to determine the converter maximum

input RMS current and assume it would all be supplied by the input capacitors. This approach works well for converters that employ a filtering inductor on their inputs. In these types of converters, all of the RMS current is supplied by the input capacitors. For converters that do not employ an input inductor, such as the reference design on the ISL6520EVAL1 board, the conservative approach may be too costly. The number of capacitors may be decreased by assuming that only 50% of the RMS current is supplied by the input capacitors. This approach will usually provide enough capacitors to provide proper power decoupling.

The voltage rating at maximum ambient temperature should be 1.25 to 1.5 times the maximum input voltage. More conservative approaches can bring the voltage rating up to 2 times the maximum input voltage. High frequency decoupling, which is highly recommended, is implemented through the use of ceramic capacitors in parallel with the bulk capacitor filtering.

The reference design utilizes Sanyo 330 $\mu$ F, 6.3V POSCAP capacitors as the bulk input capacitors (Sanyo Part Number 6TPB330M). Each of these capacitors has a 3A<sub>RMS</sub> maximum allowable ripple current rating. The number of capacitors used in each design, which is shown in Table 1, is more than sufficient to handle the input RMS current under the assumption that only 50% of that current is being supplied by the input capacitance.

### **MOSFET Selection**

The ISL6520EVAL1 board can accommodate multiple MOSFET package styles. Each placeholder can accommodate DPAK or D2PAK package connections. The output loading and the thermal environment ultimately dictate the MOSFET selected. While many factors are involved in the selection of the MOSFETs, overall efficiency of the regulator should be a major contributor. There are three major aspects of power loss that are associated with the MOSFET. These are gate drive power losses, conduction losses, and switching losses.

TABLE 1. ISL6520EVAL1 DESIGN RECOMMENDATIONS

|                                 | REFERENCE   | MAXIMUM LOAD CURRENT               |                                    |                                    |  |

|---------------------------------|-------------|------------------------------------|------------------------------------|------------------------------------|--|

| COMPONENTS                      | DESIGN      | DESIGN A - 5A                      | DESIGN B - 10A                     | DESIGN C - 15A                     |  |

| MOSFETS                         | Q1, Q2      | FAIRCHILD HUF76121D3S              | FAIRCHILD HUF76129D3S              | FAIRCHILD HUF76143S3S              |  |

| Inductor                        | L1          | 6.4μΗ<br>Panasonic<br>ETQP6F6R4HFA | 3.2µH<br>Panasonic<br>ETQP6F3R2HFA | 2.0µH<br>Panasonic<br>ETQP6F2R0LFA |  |

| Number of Input<br>Capacitors   | C12, C13    | 1                                  | 1                                  | 2                                  |  |

| Number of Output Capacitors     | C8, C9, C10 | 1                                  | 2                                  | 3                                  |  |

| Number of Decoupling Capacitors | C5A, C5B    | 1                                  | 1                                  | 2                                  |  |

| OCSET Resistor                  | R5          | 9.06kΩ                             | 12.7kΩ                             | 6.34kΩ                             |  |

Gate Drive Power Losses result in the power dissipated within the gate drivers, which are located in the ISL6520 and ISL6520A. This power loss is a result of displacing the charge on the gate-to-source capacitance, Cgs.

The gate power is frequency dependent and is determined by the equation:

$$P_{gate} = (Q_{gu}xV_{gu} + Q_{gl}xV_{gl})xF_{s}$$

where

Q<sub>qu</sub> = Upper MOSFET gate charge

V<sub>gu</sub> = Upper MOSFET gate voltage

Q<sub>al</sub> = Lower MOSFET gate charge

V<sub>gl</sub> = Lower MOSFET gate voltage

Conduction Losses are simply I<sup>2</sup>R losses. Conduction losses can be approximated as:

$$P_{condu} = R_{dsu} x D x I_{LOAD}^{2}$$

$$P_{condl} = R_{dsl} x (1 - D) x I_{LOAD}^{2}$$

where

$P_{condu}$  = Upper MOSFET Conduction Loss

P<sub>condl</sub> = Lower MOSFET Conduction Loss

R<sub>dsu</sub> = Upper MOSFET R<sub>DS(on)</sub>

R<sub>dsl</sub> = Lower MOSFET R<sub>DS(on)</sub>

D = Duty Cycle

I<sub>load</sub> = Load Current

Note that the Rds(on) will increase as the junction temperature of the MOSFET increases. This increase in impedance should be taken into account when calculating the conduction losses.

Switching losses are caused by crossover conduction during the switching interval and by the output capacitance, Coss, being displaced. Since the dissipation caused by the output capacitance is very small compared to the loss due to crossover conduction, it can be ignored.

The ISL6520A can introduce switching losses that the ISL6520 will not. Since the ISL6520A gives the converter the ability to sink current, the lower MOSFET will experience switching losses when the converter is in a current sinking state. Since the ISL6520A can switch fluidly from a current sourcing state to a current sinking state and back again, it is prudent to assume a worst case condition of full time current sourcing and sinking when sizing the upper and lower MOSFETs, respectively. The equations shown below give a simplified, yet useful, representation of switching loss for a MOSFET

$$P_{switch} = \frac{1}{2}xV_{in}xI_{in}xt_{sw}xf_{s}$$

where

V<sub>in</sub> = Input Voltage

I<sub>in</sub> = Input Current

tsw = MOSFET switching time

f<sub>s</sub> = Switching Frequency

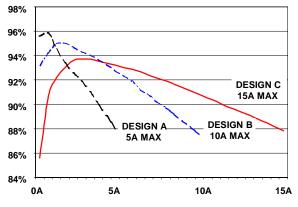

## ISL6520EVAL1 Efficiency

Figure 3 shows the efficiency of the ISL6520EVAL1 for all three design recommendations: 5A maximum load, 10A maximum load, and 15A maximum load respectively. As can be seen in the efficiency curves, the MOSFETs and other components were selected so as to keep a high efficiency throughout the load range of the converter.

FIGURE 3. ISL6520EVAL1 EFFICIENCY

# **Output Voltage Programming**

Simple resistor value changes allow for outputs as low as 0.8V or as high as the input voltage. The steady state DC output voltage can be set using the following formula:

$$V_{out} = V_{ref} x \left( 1 + \frac{R1}{R4} \right)$$

where

V<sub>out</sub> = Desired output voltage of converter

$V_{ref} = ISL6520$  internal reference (0.8V)

The output voltage of the reference designs presented in this application note is 3.3V.

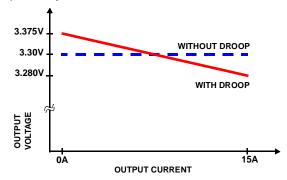

# Lossless Output Voltage Droop with Load

The ISL6520EVAL1 board has unpopulated component footprints in place to implement output voltage droop. Droop is an intentional sag in the output voltage that is proportional to the output current. Although not necessary for proper circuit operation, utilizing droop allows the dynamic regulation to be improved by taking advantage of static regulation requirements and expanding the available headroom for transient edge output excursions. In practical applications that are compared to a non-droop

implementation, the droop implementation requires fewer output capacitors or better regulation with the same type and number of output capacitors.

By moving the regulation point ahead of the output inductor (at the PHASE node), droop becomes equal to the average voltage drop across the output inductor's DC resistance as well as any distributed resistance. The droop circuitry is simply an RC low pass filter placed across the output inductor. This filter must have the same time constant that the output inductor and it's corresponding DCR have. The design must be careful to include any parasitic impedances of the PC board if the DCR of the inductor is very low.

On the ISL6520EVAL1 board, this filter is represented by resistors R6 and R7 and capacitor C7. Resistor R7 can be used to scale the magnitude of the droop. The output of this low pass filter is fed directly into the feedback compensation network of the regulator. The effects of this filter on the frequency response of the converter is minimal and can be ignored when evaluating the frequency response of the converter. To insure symmetric output voltage excursions about the set voltage in response to load transients, the output voltage should be programmed to be above the nominal level by half the calculated droop.

As supplied, the ISL6520EVAL1 does not employ droop. A successful droop implementation has been designed and tested for Design C. The DCR of the output inductor is  $5m\Omega$ . This gives a time constant of:

$$\tau = \frac{L_{out}}{DCR + R_{parasitic}} = 400 \mu S \qquad \text{with } R_{parasitic} = 0 \Omega$$

The impedance portion of the time constant calculation for the RC filter includes the parallel combination of the filter resistor, R6, and the feedback resistor, R1. A value for R6 is chosen that will not significantly decrease the impedance already set by R1. A  $16.2k\Omega$  resistor was chosen. This yields an effective impedance of  $2.64k\Omega$ . The filter capacitor, C7, is then calculated:

$$\tau = RxC = 2644xC = 400 \mu S$$

$$C \sim 0.1 \mu F$$

Since the regulation point is now located at the phase node, and a  $16.2 k\Omega$  resistor is being added to the DC path for regulation, then the resistor, R4, used to program the output voltage must be adjusted. The maximum output current for Design C is 15A and the DCR of the inductor is  $5 m\Omega$ . This combination will yield a total droop of 75 mV. In order to center the droop symmetrically about the 3.3 V set point, the no load set point will be 3.375 V. The corresponding value for R4 to accomplish this is  $6.04 k\Omega$ .

Figure 4 shows the output voltage of the converter with the droop circuitry added.

FIGURE 4. OUTPUT VOLTAGE DROOP

Component Values for Droop Implementation:

$R6 = 16.2k\Omega$

R7 = Not Populated

$C7 = 0.1 \mu F$

$R4 = 6.04k\Omega$

With the proper selection of the components used in the RC filter actoss the inductor, the frequency response of the system is only minimally affected and the compensation network does not need to be recalculated.

### **Output Capacitor Selection**

The shape of the output voltage waveform during a load transient that represents the worst case loading conditions will ultimately determine the number of output capacitors and their type. When this load transient is applied to the converter, most of the energy required by the load is initially delivered from the output capacitors. This is due to the finite amount of time required for the inductor current to slew up to the level of the output current required by the load. This phenomenon results in a temporary dip in the output voltage. At the very edge of the transient, the Equivalent Series Inductance (ESL) of each capacitor induces a spike that adds on top of the existing voltage drop due to the Equivalent Series Resistance (ESR)

After the initial spike, attributable to the ESR and ESL of the capacitors, the output voltage experiences sag. This sag is a direct consequence of the amount of capacitance on the output.

During the removal of the same output load, the energy stored in the inductor is dumped into the output capacitors. This energy dumping creates a temporary hump in the output voltage. This hump, as with the sag, can be attributed to the total amount of capacitance on the output.

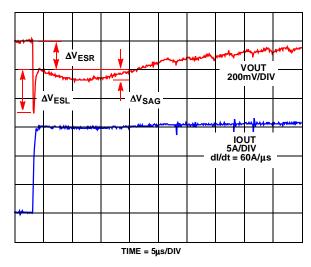

#### FIGURE 5. TRANSIENT RESPONSE

Figure 5 shows a typical response of the ISL6520EVAL1 to a load transient. The current slew rate was made large to show the effects of the parasitic inductances in the output stage.

The amplitudes of the different types of voltage excursions can be approximated by using the following formulae

$$\Delta V_{\text{ESR}} = \text{ESRxI}_{\text{tran}} \qquad \Delta V_{\text{ESL}} = \text{ESLx} \frac{\text{dI}_{\text{tran}}}{\text{dt}}$$

$$\Delta V_{\text{SAG}} = \frac{L_{\text{out}} x I_{\text{tran}}^{2}}{C_{\text{out}} x (V_{\text{in}} - V_{\text{out}})}$$

$$\Delta V_{\text{HUMP}} = \frac{L_{\text{out}} x I_{\text{tran}}^{2}}{C_{\text{out}} x V_{\text{out}}}$$

where

Itran = Output Load Current Transient

Cout = Total Output Capacitance

In a typical converter design, the ESR of the output capacitor bank dominates the transient response. The ESR and the ESL are typically the major contributing factors in determining the output capacitance. The number of output capacitors can be determined by using the following equation that relates the ESR and ESL of the capacitors to the transient load step and the voltage limit ( $\Delta$ Vo):

$$\mbox{Number of Caps} \, = \, \frac{\mbox{ESLx} \Delta \mbox{I}_{tran}}{\mbox{dt}} + \mbox{ESRx} \mbox{I}_{tran}}{\mbox{}_{o}} \label{eq:Number}$$

If  $\Delta V$ sag and/or  $\Delta V$ hump are found to be too large for the output voltage limits, then the amount of capacitance may need to be increased. In this situation, a trade off between output inductance and output capacitance may be necessary.

The ESL of the capacitors, which is an important parameter in the above equations, is not usually listed in databooks.

Practically, it can be approximated if an Impedance Vs. Frequency curve is given for a specific capacitor:

$$ESL = \frac{1}{C}x(2x\pi x f_{res})^2$$

where  $f_{res}$  is the frequency where the lowest impedance is achieved (resonant frequency).

The ESL of the capacitors becomes a concern when designing circuits that supply power to loads with high rates of change in the current.

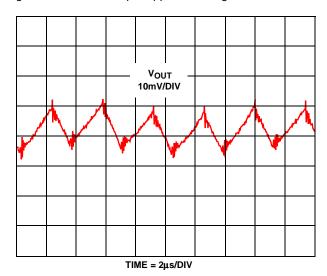

## Output Voltage Ripple

The amount of ripple voltage on the output of the DC-DC converter varies with the input voltage, switching frequency, output inductor, and output capacitors. For a fixed switching frequency and output filter, the voltage ripple increases with the input voltage. The ripple content of the output voltage can be estimated with the following equation:

$$\Delta V_{out} = \Delta I_{L} x E S R$$

where

$$\Delta I_{L} = \frac{(V_{in} - V_{out})x \frac{V_{out}}{V_{in}}}{L_{out}xf_{s}}$$

If the output capacitors have already been selected to meet certain transient requirements, then the ripple voltage can be set by the output inductance.

Figure 6 shows the output ripple for Design C.

FIGURE 6. OUTPUT VOLTAGE RIPPLE

### **Conclusion**

The ISL6520EVAL1 board is a DC-DC converter reference design that is flexible enough to accommodate a wide range of output current requirements. The printed circuit board is laid out to accommodate the necessary components for operation from low load levels to 15A of output current.

### References

For Intersil documents available on the web, see www.intersil.com/

- [1] ISL6520 Data Sheet, Intersil Corporation, Doc. # 9009

- [2] ISL6520A Data Sheet, Intersil Corporation, Doc. # 9016

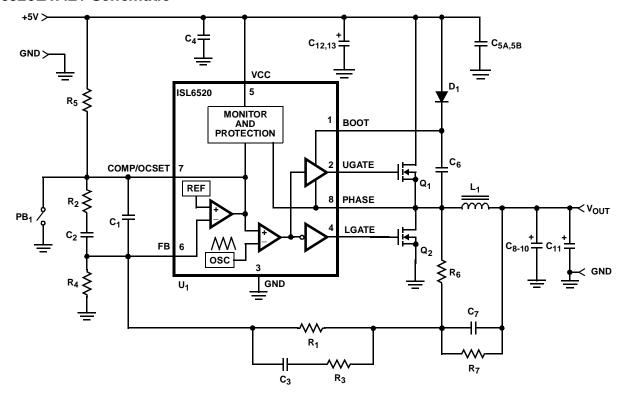

### ISL6520EVAL1 Schematic

TABLE 2. ISL6520EVAL1 BILL OF MATERIAL

| REF DES            | DESCRIPTION                            | VENDOR    | VENDOR P/N   | QTY |

|--------------------|----------------------------------------|-----------|--------------|-----|

| C1                 | 470pF Capacitor, 0603                  | Various   |              | 1   |

| C2                 | 8200pF Capacitor, 0603                 | Various   |              | 1   |

| C3                 | 18000pF Capacitor, 0603                | Various   |              | 1   |

| C4,C6,C11          | 0.1μF Capacitor, 0603                  | Various   |              | 2   |

| C5A,C5B            | 1μF Capacitor, 0805                    | Various   |              | 2   |

| C7                 | Not Populated Capacitor, 0603          |           |              |     |

| C8-10, C12,<br>C13 | 330μF Capacitor                        | Sanyo     | 6TPB330M     | 5   |

| D1                 | Diode, 30mA, 30V                       | Digikey   | MA732        | 1   |

| L1                 | 2μH Inductor                           | Panasonic | ETQP6F2ROLFH | 1   |

| Q1, Q2             | MOSFET                                 | Fairchild | HUF76143S3S  | 2   |

| R1                 | 3.16kΩ 1% Resistor, 0603               | Various   |              | 1   |

| R2                 | 10.0kΩ 1% Resistor, 0603               | Various   |              | 1   |

| R3                 | 60.4Ω 1% Resistor, 0603                | Various   |              | 1   |

| R4                 | 1.00kΩ Resistor, 0603                  | Various   |              | 1   |

| R5                 | 6.34kΩ Resistor, 0603                  | Various   |              | 1   |

| R6                 | Not Populated Resistor, 0603           |           |              |     |

| R7                 | 0Ω Resistor, 0603                      | Various   |              | 1   |

| PB1                | Pushbutton, miniature                  | Digikey   | P8007S-ND    | 1   |

| U1                 | Single Synchronous Buck PWM Controller | Intersil  | ISL6520CB    | 1   |

| TP1,2,3,4          | Test Points                            | Keystone  | 1514-2       | 4   |

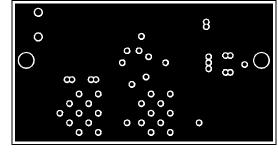

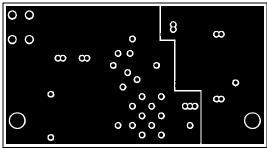

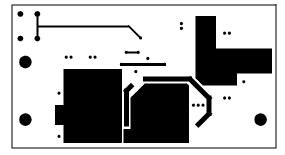

# **Board Description**

**Top Layer**

**Ground Layer**

**Power Layer**

**Bottom Layer**

All Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at website <a href="https://www.intersil.com/design/quality">www.intersil.com/design/quality</a>

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intesil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web sit ewww.intersil.com